Выбирая память, следует думать отнюдь не только о ее частоте, как это делают многие, но и обратить внимание на тайминги. В этой статье мы расскажем о том, почему этот параметр не менее, а то и более важен.

Разбираемся с теорией

Частота оперативной памяти определяет скорость передачи данных за единицу времени. Высокая частота обычно ассоциируется с более быстрой работой и повышенной производительностью. Однако, при увеличении частоты, растет вероятность возникновения ошибок из-за т.н. паразитных емкостей, что может снизить стабильность системы. Паразитные емкости в оперативной памяти представляют собой нежелательные электрические характеристики, которые могут влиять на работу памяти и вызывать ошибки в передаче данных. Эти емкости могут возникать из-за различных факторов, включая конструкцию памяти, материалы, из которых она изготовлена, и окружающие условия.

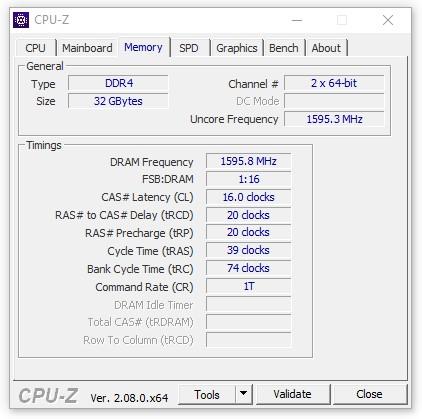

Тайминги оперативной памяти, с другой стороны, определяют количество тактов, необходимых для различных операций доступа к памяти. Они включают в себя такие параметры, как CAS Latency (CL), RAS to CAS Delay (tRCD), RAS Precharge (tRP), и Row Activate Time (tRAS). Каждый из этих таймингов влияет на различные аспекты процесса доступа к данным, начиная от инициации операции чтения/записи до фактического получения данных. Давайте разберем их более детально.

CAS Latency (CL)

CAS Latency указывает на количество тактов между отправкой команды на чтение или запись и фактическим выполнением этой команды. Меньшее значение CL соответствует более быстрой оперативной памяти, поскольку меньшее количество тактов требуется для доступа к данным.

RAS to CAS Delay (tRCD)

Этот параметр отвечает за количество тактов, необходимых для доступа к ячейке памяти после выбора строки (RAS) и передачи команды на чтение или запись (CAS). Он важен для эффективной организации доступа к данным в определенной строке памяти.

RAS Precharge (tRP)

Определяет количество тактов, требуемых для завершения текущей операции и перехода к следующей строке данных. Прежде чем прочитать или записать данные из следующей строки, текущую необходимо дозарядить и закрыть. Этот параметр влияет на скорость доступа к последующим данным и может оказывать существенное влияние на производительность.

Row Activate Time (tRAS)

Отвечает за количество тактов, отведенных контроллеру памяти для работы с данными в выбранной строке. Этот параметр определяет период, в течение которого контроллер остается активным в текущей строке памяти перед переключением на другую. Он также оказывает влияние на общую производительность оперативной памяти.

Помимо этих основных таймингов, существуют и другие параметры, влияющие на производительность памяти, такие как Command Rate (CR) и Voltage (V). Но именно CL, tRCD, tRP и tRAS часто используются для оценки производительности и сравнения различных модулей оперативной памяти.

Так в чем же важность таймингов оперативки

Тайминги имеют более прямое влияние на скорость доступа к данным, нежели частота. Например, CL определяет количество тактов между отправкой команды на чтение/запись и ее выполнением, тогда как tRCD определяет количество тактов для доступа к ячейке. Эти задержки напрямую влияют на скорость передачи данных, и, следовательно, на общую производительность системы.

Так что, хотя частота оперативной памяти важна для общей производительности системы, тайминги играют очень большую роль в оптимизации скорости доступа к данным. Выбор модуля памяти с более низкими и оптимально настроенными таймингами может значительно повысить эффективность работы системы, что делает их важнее частоты при выборе компонентов для сборки или апгрейда компьютера.

Чтобы лучше понять эту тему приведем простой пример. Возьмем два модуля: один с частотой 3200 МГц и таймингами 18-22-22-42, и другой с частотой 3600 МГц и таймингами 20-26-26-46. Модуль с частотой 3600 МГц имеет CL 20, тогда как модуль с 3200 МГц имеет CL 18. Таким образом, на первый взгляд модуль с более высокой частотой кажется быстрее.

Однако, если мы посмотрим на общее количество тактов, необходимых для выполнения всех основных операций доступа к памяти, включая tRP и tRCD, мы увидим, что модуль с более низкой частотой выигрывает. Это происходит потому, что при более высокой частоте, общее количество тактов на выполнение операций оказывается больше.